在半導體行業不斷追求 “更小、更快、更節能” 的發展歷程中,傳統二維平面封裝技術逐漸面臨物理極限的挑戰。當芯片制程逼近原子尺度,單純依靠縮小晶體管尺寸來提升性能的難度與成本呈指數級增長,而三維堆疊封裝設計的出現,為這一困境提供了關鍵解決方案。

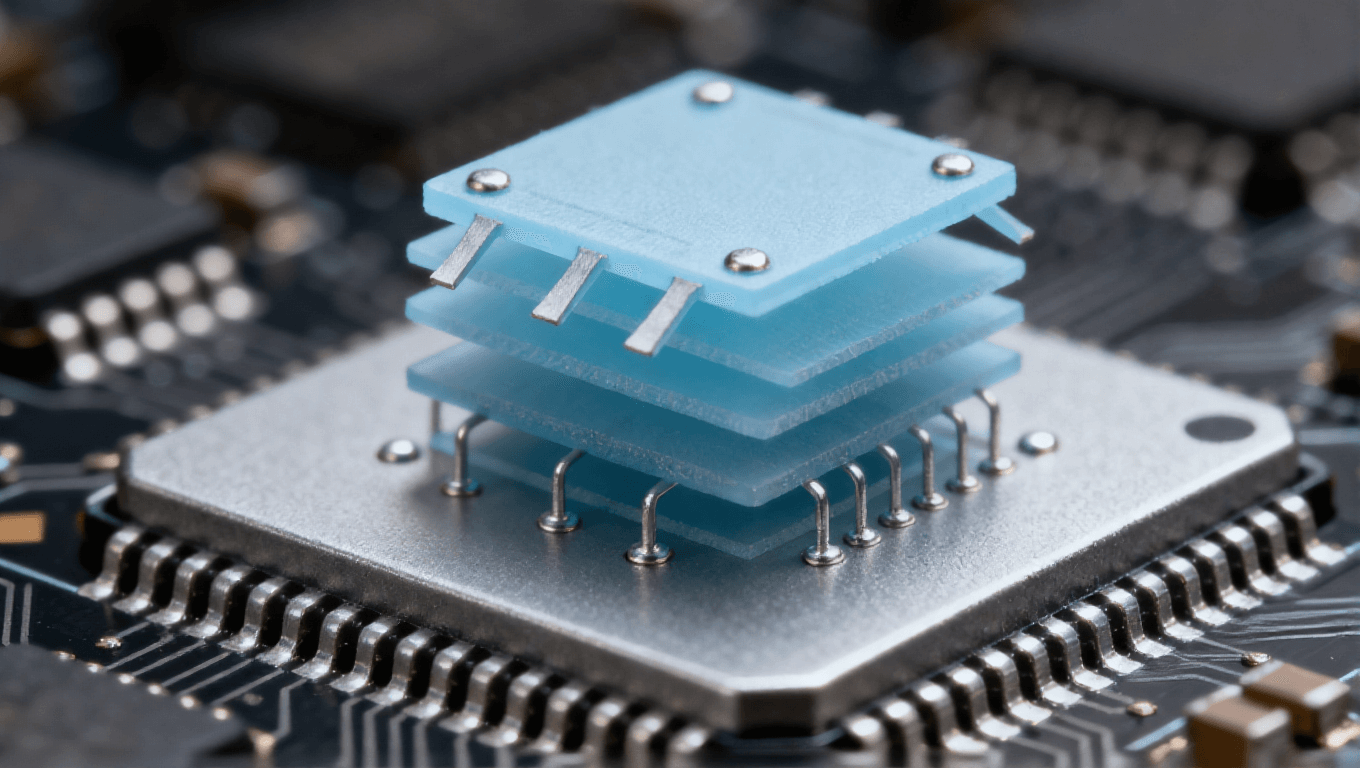

三維堆疊封裝設計(3D Stacked IC Packaging)是指通過垂直方向上的堆疊集成,將多顆芯片、芯片與無源器件或不同功能的晶圓緊密結合,形成一個高度集成的系統級封裝(SiP)結構。與傳統二維封裝相比,其核心價值體現在三個維度:一是空間利用率的飛躍,垂直堆疊使封裝面積減少 40%-60%,尤其適配智能手機、可穿戴設備等小型化終端;二是互連效率的提升,芯片間垂直互連距離縮短至微米級,信號傳輸延遲降低 30% 以上,同時功耗減少 20%-35%;三是功能集成的靈活性,可實現邏輯芯片、存儲芯片、射頻芯片等異質器件的一體化集成,快速滿足復雜系統需求。

從行業發展來看,三維堆疊封裝設計已從概念驗證階段進入規模化應用階段。根據 SEMI 數據,2024 年全球三維堆疊封裝市場規模突破 80 億美元,預計 2028 年將達到 180 億美元,年復合增長率超 20%。這一增長背后,是消費電子、汽車電子、人工智能等領域對高性能、高密度封裝的迫切需求,也印證了三維堆疊封裝設計成為半導體產業鏈核心競爭力的事實。

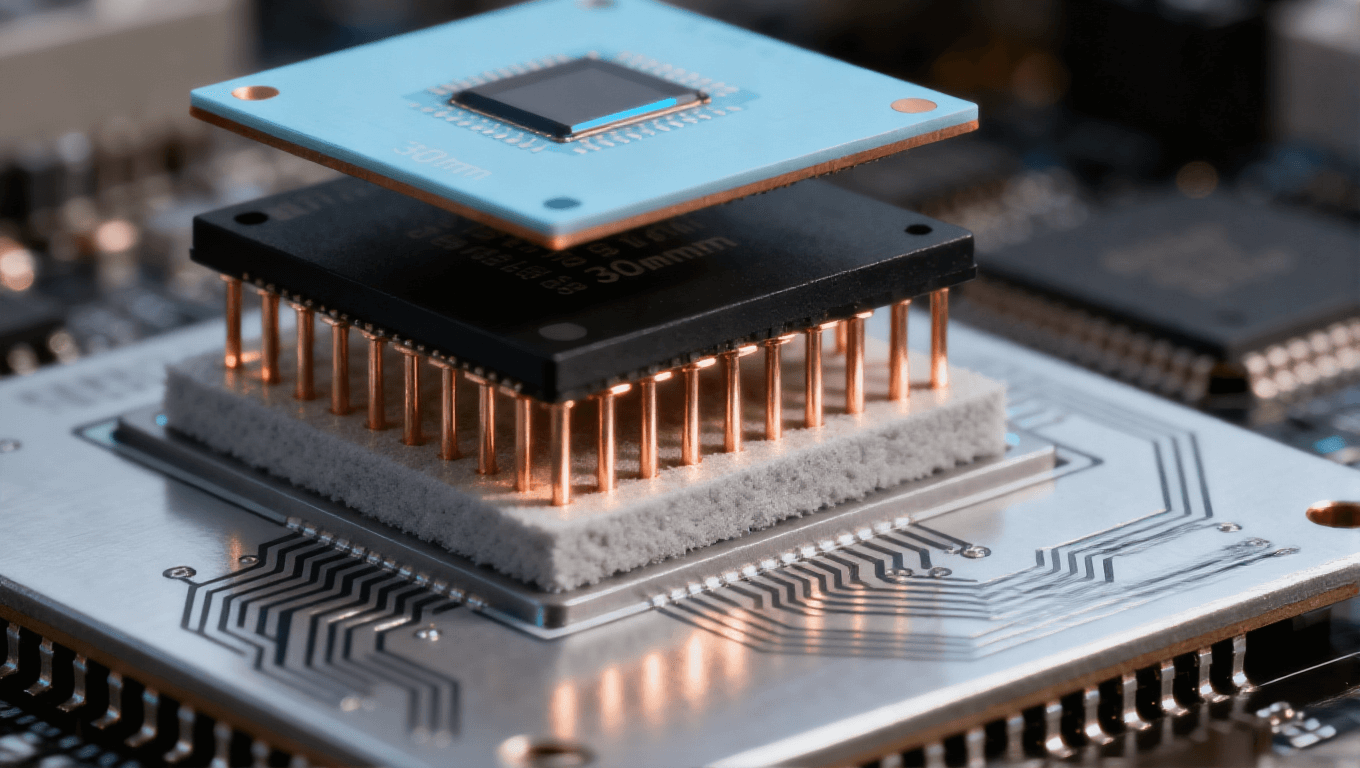

三維堆疊封裝設計并非單一技術,而是由多個核心技術模塊協同構成的復雜體系。其中,硅通孔(TSV)技術、微凸點(Micro Bump)技術與晶圓鍵合(Wafer Bonding)技術共同構成了垂直互連的基礎,也是決定封裝性能的關鍵環節。

硅通孔技術是三維堆疊封裝的核心支撐,其原理是在硅晶圓上鉆出直徑為 5-50 微米的微小通孔,通過金屬化處理(通常為銅電鍍)形成垂直導電通道,實現上下晶圓或芯片的電氣連接。相較于傳統的引線鍵合(Wire Bonding),TSV 技術的優勢在于:

1. 互連距離極短,僅為傳統引線鍵合的 1/100-1/10,大幅降低信號衰減與傳輸延遲;

2. 可實現高密度互連,每平方毫米可容納數百個通孔,滿足多芯片集成的信號需求;

3. 支持 “面對面”“背靠背” 等多種堆疊方式,靈活適配不同器件組合。

TSV 技術的工藝流程主要包括四個步驟:首先是 “通孔刻蝕”,通過深反應離子刻蝕(DRIE)在硅晶圓上形成高深寬比(通常為 10:1-30:1)的通孔;其次是 “絕緣層沉積”,在通孔內壁覆蓋二氧化硅(SiO?)或氮化硅(Si?N?),防止電流泄漏;然后是 “種子層制備”,采用物理氣相沉積(PVD)工藝沉積鈦 / 銅種子層,為后續金屬化做準備;最后是 “銅電鍍填充”,通過電化學沉積將銅填滿通孔,形成導電通道。

若說 TSV 是垂直互連的 “橋梁”,微凸點則是連接不同芯片的 “精密接口”。在三維堆疊封裝中,當芯片或晶圓需要面對面堆疊時,微凸點負責實現上下芯片的直接電氣連接,其尺寸通常在 20-50 微米,間距(Pitch)可縮小至 40 微米以下,遠小于傳統焊球(C4 Bump)的尺寸(100 微米以上)。

微凸點技術的核心挑戰在于 “高精度” 與 “高可靠性”。從工藝角度看,其制備流程包括:

1. 凸點下金屬化(UBM):在芯片焊盤上沉積鉻 / 銅 / 金或鈦 / 鎳 / 金多層金屬,增強焊盤與凸點的結合力,防止金屬擴散;

2. 凸點成型:采用電鍍工藝制備錫銀(SnAg)、銅(Cu)或金(Au)凸點,確保凸點高度均勻、形貌一致;

3. 回流焊接:通過加熱使凸點融化,與對接芯片的焊盤形成可靠的金屬間化合物(IMC),實現電氣與機械連接。

為應對微凸點的可靠性問題,行業通常采用 “-underfill(底部填充)” 工藝,在凸點間隙注入環氧樹脂,吸收熱應力與機械應力,避免凸點在溫度循環或振動環境下斷裂。

晶圓鍵合技術是將兩片或多片晶圓在特定條件下(溫度、壓力、真空)緊密結合的工藝,確保三維堆疊結構的機械穩定性與封裝氣密性。根據鍵合材料的不同,主流技術可分為 “直接鍵合” 與 “中介層鍵合” 兩類:

? 直接鍵合:無需額外粘合劑,通過晶圓表面的原子間作用力(如范德華力、共價鍵)實現結合,典型代表是 “硅 - 硅直接鍵合(SDB)” 與 “氧化硅 - 氧化硅鍵合(SiO?-SiO?)”。該技術的優勢是鍵合強度高、界面電阻低,適用于對性能要求苛刻的場景(如圖像傳感器、射頻器件);

? 中介層鍵合:通過聚合物(如聚酰亞胺、苯并環丁烯)或金屬層實現晶圓連接,工藝溫度低(通常低于 300℃),兼容性強,適合異質晶圓(如硅晶圓與化合物半導體晶圓)的堆疊。

無論采用哪種鍵合方式,“對準精度” 都是核心指標。目前行業主流的對準設備可實現 ±0.5 微米的對準誤差,而隨著堆疊層數增加(如 4 層以上堆疊),對準誤差的累積會直接影響互連可靠性,因此 “分步對準” 與 “誤差補償算法” 成為高端三維堆疊封裝設計的關鍵技術難點。

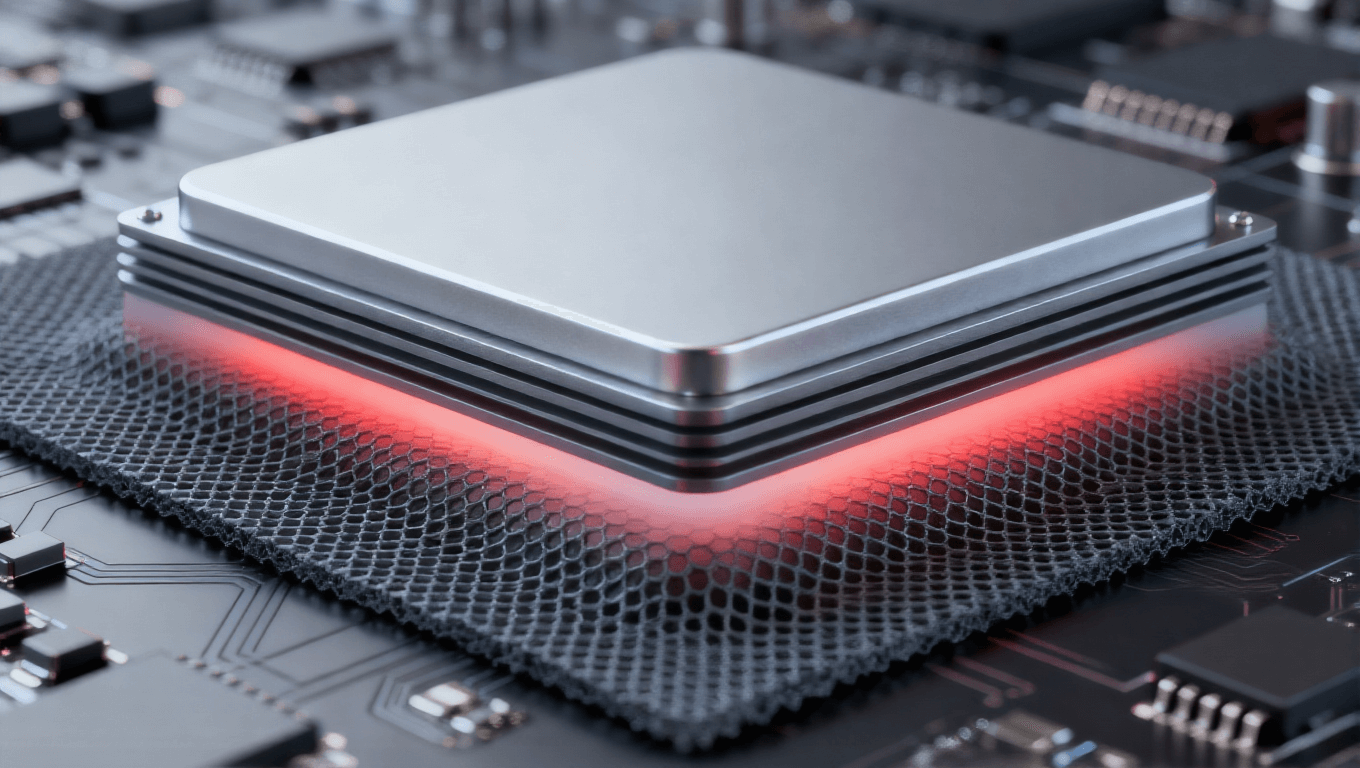

盡管三維堆疊封裝設計優勢顯著,但在實際量產過程中,仍面臨熱管理、對準精度、可靠性測試三大核心工藝難點。這些難點不僅影響產品良率,更直接決定了技術的應用范圍,因此行業內已形成一系列針對性的解決方案。

三維堆疊封裝將多顆芯片垂直堆疊,使單位體積內的功率密度大幅提升(部分高端產品功率密度可達 50W/cm3 以上),而芯片(尤其是邏輯芯片、AI 芯片)在工作時會產生大量熱量。若熱量無法及時散出,芯片溫度會快速升高,導致性能下降(如 CPU 頻率降頻)、壽命縮短,甚至出現燒毀風險。

熱管理難點的核心原因有兩個:一是垂直堆疊結構使熱量難以通過傳統的 “底部散熱” 方式導出,熱量在堆疊層間積聚;二是異質集成場景下(如邏輯芯片與存儲芯片堆疊),不同芯片的熱膨脹系數(CTE)差異較大,溫度變化會導致層間產生熱應力,進一步加劇可靠性問題。

針對這一難點,行業已形成 “主動散熱 + 被動散熱” 結合的解決方案:

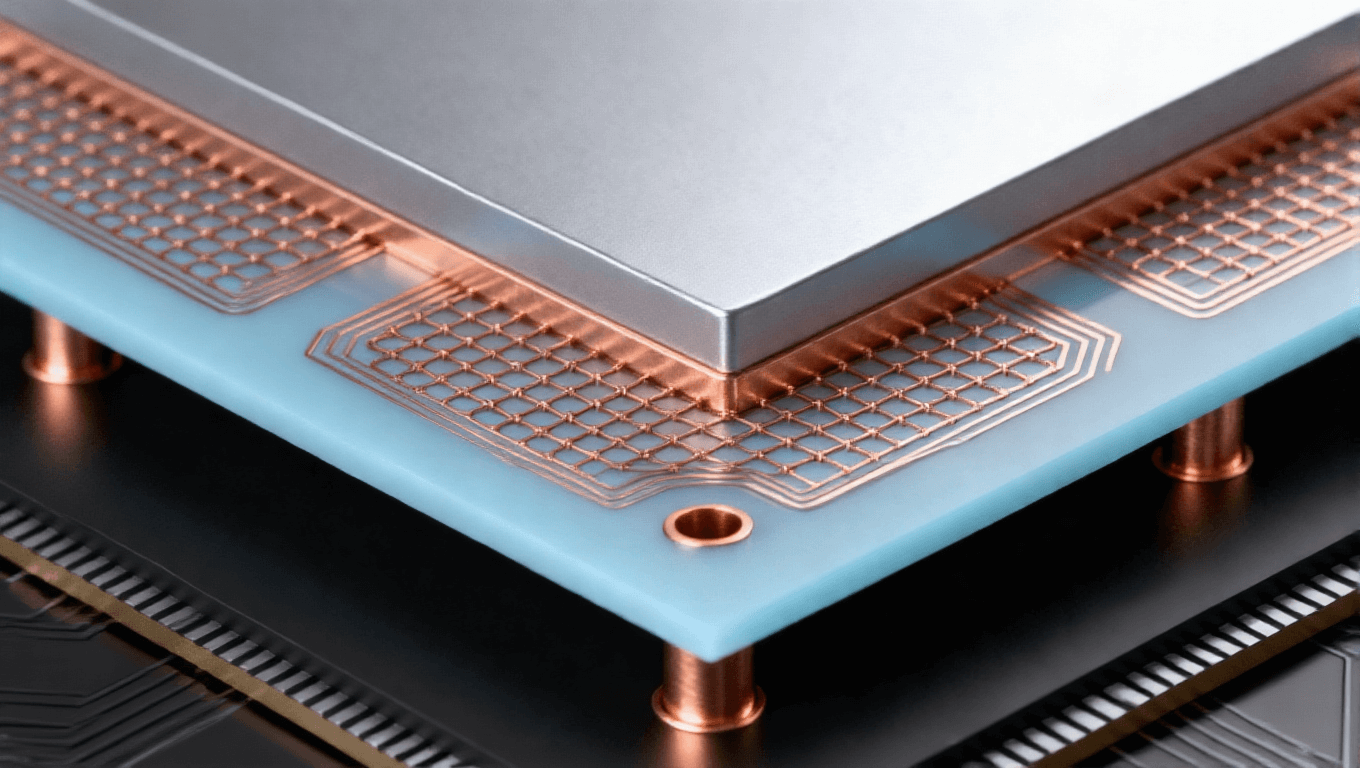

1. 被動散熱優化:在堆疊結構中嵌入 “熱界面材料(TIM)”,如石墨烯、納米銀漿,提升層間熱傳導效率;同時采用 “散熱頂蓋(Heat Spreader)” 設計,將堆疊芯片的熱量傳導至外部散熱系統;

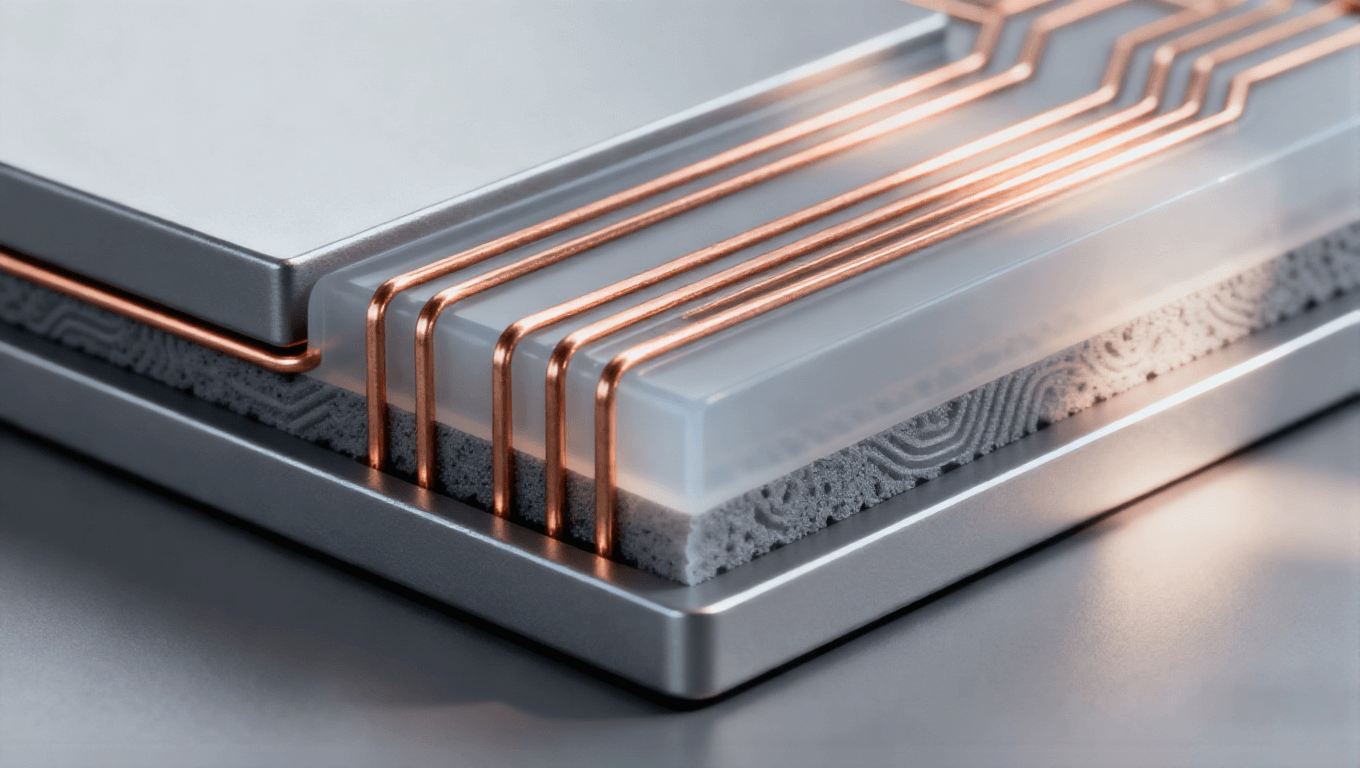

2. 主動散熱創新:對于高功率場景(如 AI 服務器芯片),引入 “微流道散熱” 技術,在晶圓或封裝內設計微小流道,通過冷卻液循環帶走熱量;部分廠商還嘗試將 “熱電冷卻器(TEC)” 集成到封裝中,通過半導體溫差效應主動降溫;

3. 設計層面優化:采用 “非對稱堆疊” 布局,將高發熱芯片(如邏輯芯片)放置在靠近散熱端的位置,低發熱芯片(如存儲芯片)放置在內部,減少熱量傳遞路徑;同時通過芯片分區供電、動態功耗管理,降低局部熱點溫度。

在三維堆疊封裝設計中,每增加一層堆疊,就需要一次晶圓或芯片的對準與鍵合。由于設備精度、材料變形等因素,每次對準都會產生微小誤差(通常為 ±0.1-±1 微米),而誤差的累積會導致上下層的 TSV 或微凸點無法精準對接,進而出現開路、短路等問題,嚴重影響良率。

對準精度難點的典型場景是 “3 層以上邏輯芯片堆疊” 與 “異質晶圓堆疊”。前者由于堆疊層數多,誤差累積效應明顯;后者由于不同晶圓的材料特性差異(如硅與碳化硅的硬度、熱膨脹系數不同),在鍵合過程中易發生變形,導致對準偏差。

為解決這一問題,行業主要從 “設備升級” 與 “工藝優化” 兩個方向突破:

1. 高精度對準設備:采用 “雙 - sided alignment(雙面對準)” 技術,通過晶圓上下兩側的攝像頭同時捕捉對準標記,實時調整晶圓位置,將單次對準誤差控制在 ±0.3 微米以內;部分高端設備還引入 “激光干涉測量” 模塊,進一步提升對準精度;

2. 誤差補償算法:在封裝設計階段,通過有限元分析(FEA)模擬鍵合過程中的材料變形,提前預留補償量;在量產階段,通過機器視覺系統實時檢測對準誤差,動態調整鍵合參數(如壓力、溫度),抵消誤差累積;

3. 中間層(Interposer)技術:引入硅或玻璃中間層,先將芯片與中間層對準鍵合,再通過中間層實現多層堆疊。中間層可作為 “緩沖層”,減少直接堆疊的對準難度,同時提升互連可靠性。

三維堆疊封裝結構復雜,包含大量垂直互連通道與異質器件,其可靠性測試面臨兩大挑戰:一是 “故障定位難”,傳統的探針測試無法覆蓋內部堆疊層,難以精準定位開路、短路等故障;二是 “測試場景多”,需要模擬高溫、低溫、濕度、振動等多種環境,驗證長期可靠性,測試周期長、成本高。

針對這些挑戰,行業已開發出一系列專用測試技術:

1. 非破壞性測試(NDT)技術:采用 “超聲掃描顯微鏡(SAM)” 檢測層間鍵合質量,通過超聲波反射信號判斷是否存在空洞、分層等缺陷;利用 “X 射線斷層掃描(X-CT)” 實現三維結構成像,直觀觀察內部互連情況;

2. 電學測試技術:開發 “晶圓級測試(Wafer-Level Test)” 方案,在堆疊前對每顆晶圓進行全面測試,篩選出不良品,減少后續封裝成本;引入 “邊界掃描測試(BST)”,通過芯片內置的測試電路,實現對內部互連通道的電學性能檢測;

3. 可靠性驗證標準:遵循 JEDEC(聯合電子設備工程委員會)制定的可靠性測試標準,如溫度循環測試(TC)、高溫高濕偏壓測試(HBM)、機械沖擊測試(MS)等,確保產品在不同應用場景下的長期穩定性。

隨著技術的成熟,三維堆疊封裝設計已在消費電子、汽車電子、人工智能與數據中心三大領域實現規模化應用,成為推動這些領域產品創新的核心技術之一。以下結合具體行業案例,分析其應用特點與價值。

消費電子(如智能手機、平板電腦、可穿戴設備)對產品尺寸與性能的要求極為苛刻,三維堆疊封裝設計恰好滿足這一需求。以智能手機為例,其核心芯片(如 AP 應用處理器、圖像傳感器)采用三維堆疊封裝后,可在縮小封裝面積的同時,提升數據傳輸速度與存儲容量。

典型案例 1:蘋果 A 系列芯片的 3D 堆疊封裝

蘋果自 A15 芯片開始,采用 “邏輯芯片 + 內存芯片” 的 3D 堆疊封裝設計(稱為 “3D IC”),將 A15 的 CPU/GPU 核心與 LPDDR5 內存垂直堆疊,封裝面積較傳統二維封裝減少約 30%,同時內存帶寬提升 50% 以上。這一設計使 iPhone 13 系列在有限的機身空間內,實現了性能與續航的雙重提升。

典型案例 2:三星圖像傳感器的 3D 堆疊

三星的 ISOCELL JN1 圖像傳感器采用 “像素層 + 邏輯層” 的 3D 堆疊設計,將負責信號處理的邏輯電路轉移到像素層下方,使傳感器尺寸縮小至 1/4 英寸(約 6.35 毫米),同時像素尺寸保持在 0.64 微米,兼顧了小型化與高畫質。該傳感器已廣泛應用于中高端智能手機的前置攝像頭與后置副攝像頭。

在消費電子領域,三維堆疊封裝設計的未來趨勢是 “多芯片異構集成”,例如將 AP、射頻芯片、電源管理芯片(PMIC)、傳感器等集成到一個封裝中,形成 “系統級封裝(SiP)”,進一步提升終端產品的集成度與性價比。

汽車電子(如自動駕駛芯片、車規級 MCU、車載雷達)對封裝的可靠性與安全性要求遠高于消費電子,需滿足 - 40℃-150℃的寬溫度范圍、10 年以上的使用壽命,以及抗振動、抗電磁干擾等嚴苛條件。三維堆疊封裝設計通過優化互連結構與材料選擇,可滿足這些 “剛性要求”。

典型案例 1:特斯拉自動駕駛芯片(HW4.0)

特斯拉 HW4.0 自動駕駛芯片采用 “2 顆 GPU 核心 + 1 顆 CPU 核心 + 多顆神經網絡加速器” 的 3D 堆疊封裝設計,通過 TSV 技術實現核心間的高速互連,數據處理能力達到 200TOPS(每秒萬億次操作)。為滿足車規可靠性要求,該封裝采用 “陶瓷基板” 替代傳統的有機基板,提升熱穩定性與抗振動能力;同時引入 “冗余互連” 設計,即使部分 TSV 出現故障,仍可通過備用通道實現信號傳輸,保障自動駕駛功能安全。

人工智能(AI)訓練與數據中心場景對芯片的算力需求呈指數級增長,而傳統二維封裝的芯片由于互連延遲高、功耗大,難以滿足需求。三維堆疊封裝設計通過 “內存與邏輯芯片的緊密集成”,大幅提升內存帶寬、降低功耗,成為 AI 芯片的核心封裝方案。

典型案例 1:英偉達 H100 GPU 的 3D V-Cache 技術

英偉達 H100 GPU 采用 “3D 堆疊緩存(V-Cache)” 設計,將 24GB 的 SRAM 緩存通過微凸點技術垂直堆疊在 GPU 核心上方,使緩存容量較上一代產品提升 3 倍,內存帶寬達到 3.3TB/s。這一設計使 H100 在 AI 訓練任務(如大語言模型訓練)中的算力提升 40% 以上,同時功耗降低 15%,有效緩解了 “內存墻” 問題(即內存速度跟不上 CPU/GPU 算力的瓶頸)。

典型案例 2:英特爾至強處理器的 3D 堆疊封裝

英特爾第 4 代至強處理器(Sapphire Rapids)采用 “邏輯芯片 + 高帶寬內存(HBM)” 的 3D 堆疊封裝,將 8 顆 HBM2e 內存芯片垂直堆疊在處理器核心旁邊,通過 TSV 技術實現高速互連,內存帶寬達到 1TB/s 以上。該設計使至強處理器在數據中心的虛擬化、云計算任務中,能夠更高效地處理大規模數據,提升服務器的整體性能。

在 AI 與數據中心領域,三維堆疊封裝設計的未來方向是 “多層堆疊與異質集成”,例如將 GPU、CPU、HBM 內存、AI 加速器集成到一個 “3D 芯片系統” 中,進一步突破算力與功耗的極限。

隨著半導體行業對高性能、高密度、低功耗封裝的需求持續增長,三維堆疊封裝設計將在技術、應用、成本三個維度呈現明確的發展趨勢,這些趨勢不僅將推動技術本身的成熟,還將重塑半導體產業鏈的競爭格局。

未來,三維堆疊封裝設計將與 7nm 以下先進制程深度融合,形成 “先進制程 + 先進封裝” 的協同創新模式。一方面,先進制程的芯片尺寸更小、性能更強,為三維堆疊提供了更優的 “積木”;另一方面,三維堆疊封裝可彌補先進制程的成本劣勢,通過 “小芯片(Chiplet)+3D 堆疊” 的組合,實現 “用成熟制程封裝替代先進制程單片” 的效果,降低成本。

同時,堆疊層數將從目前的 2-4 層向 8 層以上甚至 16 層突破。例如,臺積電已宣布開發 “3D Fabric” 技術,支持 8 層以上的晶圓堆疊;三星則在研發 “3D IC Stacking” 技術,計劃實現 16 層存儲芯片的垂直堆疊。多層堆疊將進一步提升集成度,但也對熱管理、對準精度、可靠性測試提出更高要求,推動相關配套技術的創新。

目前,三維堆疊封裝設計主要應用于高端產品(如旗艦手機芯片、AI 服務器芯片、車規級高端 MCU),但隨著技術成熟與成本下降,其應用將逐步向中低端領域滲透。例如:

? 在消費電子領域,千元機的處理器將逐步采用 “2 層堆疊封裝”,實現性能提升的同時控制成本;

? 在工業電子領域,工業 MCU、傳感器將采用三維堆疊封裝,滿足小型化、低功耗的需求;

? 在物聯網(IoT)領域,可穿戴設備、智能傳感器將通過 “3D 堆疊 + SiP” 的方式,實現多功能集成與超低功耗。

應用領域的拓展將進一步擴大三維堆疊封裝的市場規模,同時推動技術向 “定制化” 方向發展 —— 針對不同領域的需求,開發專用的堆疊方案(如工業領域的高可靠性方案、IoT 領域的低功耗方案)。

三維堆疊封裝設計作為突破半導體性能瓶頸的核心技術,通過垂直堆疊集成實現了空間利用率、互連效率與功能集成的三重突破,已成為消費電子、汽車電子、AI 與數據中心領域的關鍵支撐技術。盡管其面臨熱管理、對準精度、可靠性測試等工藝難點,但行業已形成成熟的解決方案,推動技術從高端領域向中低端領域滲透。

從行業發展來看,三維堆疊封裝設計不僅是一種封裝技術,更是半導體產業鏈 “從單一芯片競爭轉向系統級集成競爭” 的標志。未來,隨著技術與先進制程的深度融合、應用領域的持續拓展、成本的逐步下降,三維堆疊封裝設計將成為半導體行業創新的核心驅動力,為終端產品的性能升級與功能創新提供無限可能。