在 5G 通信、毫米波雷達等高頻應用場景中,射頻前端作為信號收發(fā)的核心樞紐,其 PCB 布局直接決定系統(tǒng)性能。實踐證明,不合理的布局會導致信號衰減增加 30% 以上,甚至引發(fā)自激振蕩。射頻電路的分布參數(shù)特性(趨膚效應、耦合效應)使布局設計需兼顧信號完整性、EMC(電磁兼容性)與熱管理三重目標,這與低頻數(shù)字電路存在本質差異。

當前布局設計面臨兩大挑戰(zhàn):一是 5G/6G 技術推動工作頻率向毫米波頻段(30GHz+)延伸,信號波長縮短至毫米級,對布局精度要求提升至 ±5μm;二是異構集成趨勢下,射頻模塊與數(shù)字電路的密集排布加劇了干擾問題。

1. 拓撲結構設計:射頻鏈路優(yōu)先采用 “一字形” 布局,按輸入→放大→濾波→輸出的順序排列元器件,間距嚴格遵循原理圖要求(如 π 型匹配網(wǎng)絡元件間距需<3mm)。受空間限制時可采用 “L 形” 布局,但需避免 “U 形” 布局;若必須采用,需通過隔腔屏蔽將輸入輸出端隔離,間距≥15mm。

2. 傳輸線控制:信號線長度需≤信號波長的 1/16(如 28GHz 信號最長走線僅 0.67mm),拐角采用 45° 斜切或圓弧處理,減少阻抗突變(直角拐角等效電容增加 20%)。

1. 功能分區(qū)布局:將電路劃分為射頻前端(PA/LNA)、本振(LO)、數(shù)字控制三大區(qū)域,高功率模塊(如 PA)與敏感模塊(如 LNA)間距需>信號波長的 1/2(2.4GHz 場景下≥62mm)。

2. 介質隔離措施:敏感信號(如 VCO 輸出)與干擾源之間設置接地隔離帶,寬度≥3 倍線寬;多層板中利用內層地平面實現(xiàn)垂直隔離,避免同層交叉布線。

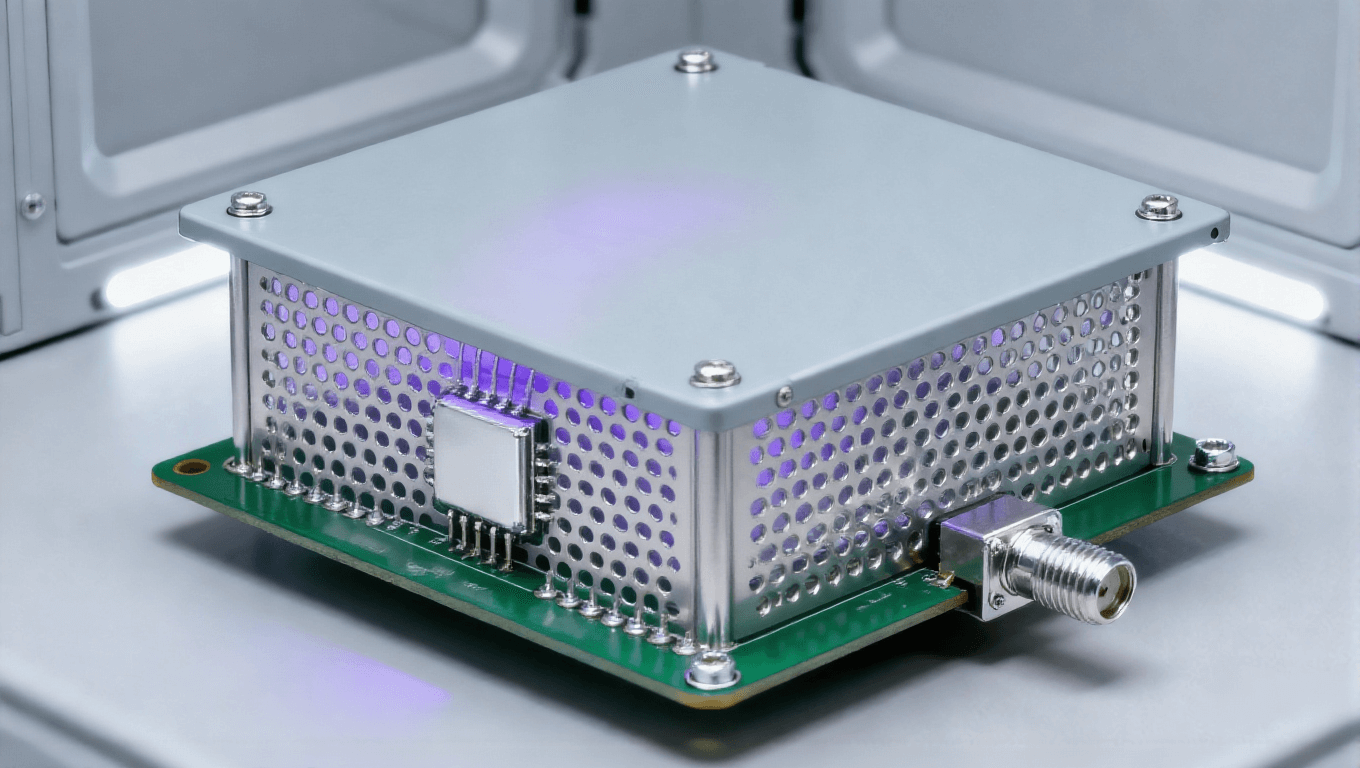

1. 接地系統(tǒng)設計:射頻區(qū)域采用多點接地方式,鋪銅間隙控制在 20-40mil,接地過孔間距≤信號波長的 1/20(10GHz 場景下≈1.5mm),且呈交錯排列。腔殼與 PCB 接觸處需開窗處理,通過兩排交錯接地孔實現(xiàn)低阻抗連接。

2. 電源去耦策略:高頻去耦電容(100pF~1nF)需緊鄰 IC 電源引腳,接地端直接通過過孔連接地平面,避免引線電感引入噪聲。電源平面采用長條狀設計,與射頻信號線平行排布,交叉處采用垂直十字結構。

1. 層疊結構設計:推薦 4 層及以上設計方案:頂層(射頻信號)、中間層(地 / 電源)、底層(輔助信號)。毫米波場景下采用 6 層結構,增加屏蔽地層減少輻射損耗。層間布線方向垂直交叉(頂層水平、底層垂直),降低信號耦合。

2. 基板材料選型:優(yōu)先選用低損耗基材,如 Rogers RO4003C(介電常數(shù) 3.55,損耗正切 0.0027)或 Taconic RF-35,替代高頻損耗較大的 FR-4。5GHz 以上場景選用 0.508mm 厚基板,毫米波場景采用超平銅箔(Rz<2μm),降低趨膚效應損耗 30%。

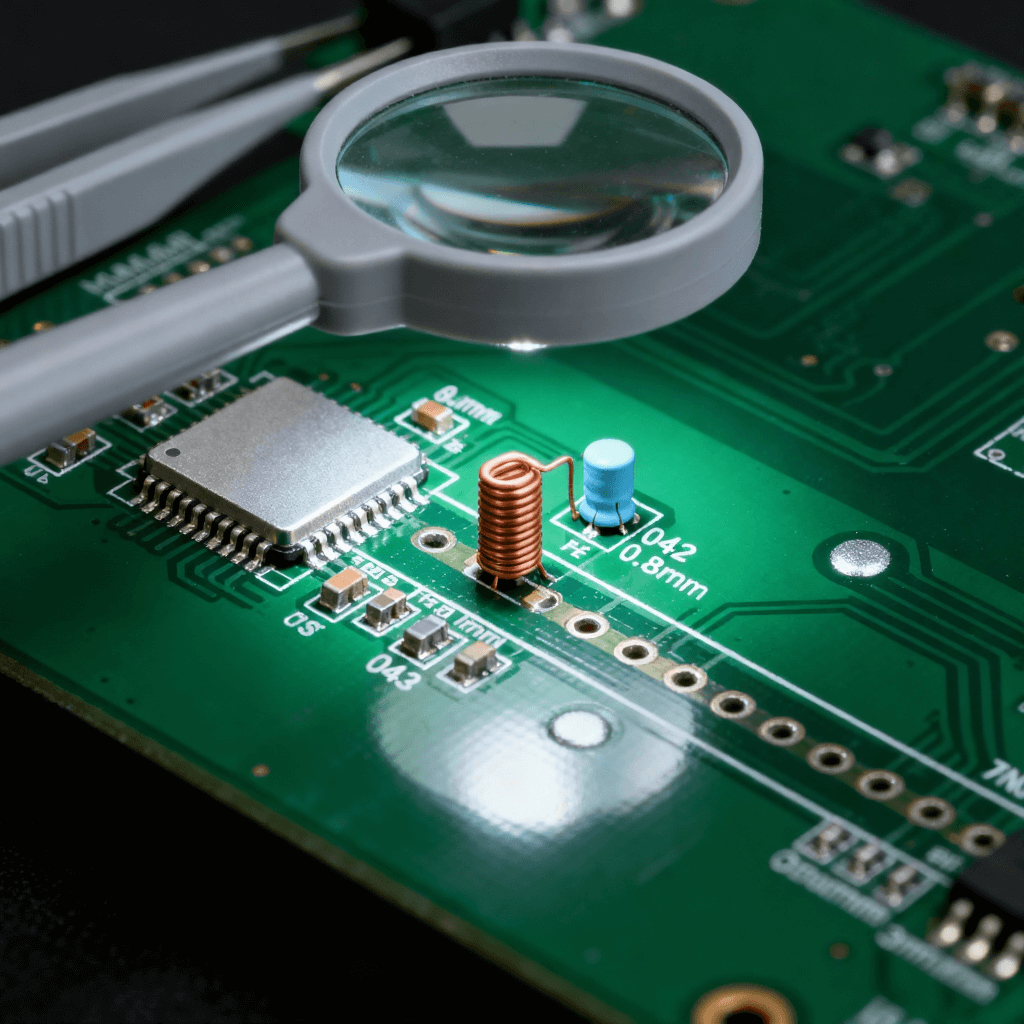

1. 有源器件布局:射頻芯片外圍電路嚴格參照 datasheet 要求,匹配元件(電感、電容)貼近引腳放置,引線長度<1mm。功率器件(如 PA)下方設置銅柱散熱,熱阻可從 40℃/W 降至 8℃/W。

2. 無源器件優(yōu)化:偏置電路的饋電電感與射頻通道垂直放置,減少互感干擾;天線饋點周圍預留 3mm 凈空區(qū),避免寄生電容影響輻射效率。

1. 電磁屏蔽措施:敏感區(qū)域采用 “過孔墻 + 金屬罩” 構成法拉第籠,過孔間距≤λ/20,隔離度可達 70dB@10GHz 以上。射頻信號線采用包地處理,地銅皮上均勻打孔,孔間距<λ/20。

2. 機械防護設計:腔殼四個角及隔腔交叉處必須設置螺釘孔,SMA 連接器旁需額外加設螺釘,防止插拔時 PCB 變形。

1. 前期仿真:利用 ANSYS HFSS 進行三維電磁仿真,優(yōu)化傳輸線阻抗與過孔布局,減少設計迭代次數(shù) 60%。通過 AI 算法自動生成匹配網(wǎng)絡,設計效率提升 40% 以上。

2. 后期驗證:制作樣板后測試 S 參數(shù)(插入損耗、回波損耗)與 EMC 指標,重點核查 1-40GHz 頻段的干擾情況,確保輻射泄漏<-50dBm。

問題類型 | 產(chǎn)生原因 | 解決措施 |

信號反射嚴重 | 阻抗突變(線寬變化、直角拐角) | 采用漸變線寬過渡,拐角改為 45° 斜切;通過仿真校準傳輸線參數(shù) |

模塊間干擾 | 高功率信號耦合至敏感電路 | 增加接地隔腔,拉大 PA 與 LNA 間距至 λ/2 以上;采用分層屏蔽設計 |

接地噪聲過大 | 地平面分割、過孔間距過大 | 采用完整地平面,接地過孔間距≤λ/20;關鍵接地焊盤就近打 3-4 個過孔 |

散熱不良 | 功率器件集中且無散熱設計 | 器件分散布局,下方設置密集散熱過孔;采用鋁基板或埋置銅塊 |

諧振現(xiàn)象 | 腔體尺寸與信號波長共振 | 邊緣添加接地過孔陣列破壞諧振模式;優(yōu)化腔殼結構避免整數(shù)倍波長尺寸 |

AI 驅動的布局工具實現(xiàn)參數(shù)化設計:輸入工作頻率、阻抗要求后,自動生成傳輸線尺寸、過孔間距與屏蔽方案,Gerber 文件精度可達 5μm。EM 仿真與布局設計實時聯(lián)動,使毫米波頻段設計周期從 3 個月縮短至 2 周。

低溫共燒陶瓷(LTCC)技術將濾波器、巴倫等元件集成至 PCB 內部,尺寸縮小至傳統(tǒng)方案的 1/10。硅基光刻工藝實現(xiàn) 100GHz 波導結構,精度達 0.1μm,為 6G 太赫茲通信奠定基礎。

環(huán)保基材(如無鉛 ENEPIG 表面處理)替代傳統(tǒng)噴錫工藝,平整度提升 10 倍的同時降低污染。異構集成技術使射頻前端與基帶芯片共封裝,布局密度提升 5 倍以上。

1. 射頻鏈路是否采用 “一字形 / L 形” 布局,輸入輸出端隔離是否達標?

2. 傳輸線阻抗是否符合 50Ω 要求,拐角是否做 45°/ 圓弧處理?

3. 接地過孔間距是否≤λ/20,地平面是否存在分割?

4. 去耦電容是否緊鄰 IC 引腳,接地路徑是否最短?

5. 高功率模塊與敏感電路間距是否>λ/2,是否采取屏蔽措施?

6. 散熱過孔與螺釘孔布局是否滿足機械與熱管理需求?

7. 是否通過仿真與實測驗證信號完整性及 EMC 性能?