在 5G 通信、汽車電子、工業控制等領域,電子設備對信號傳輸速度和穩定性的要求持續提升。多層板作為高密度電路的核心載體,其信號傳輸質量直接決定設備性能 —— 而阻抗控制技術,正是保障信號完整性的關鍵。

當信號在多層板線路中傳輸時,若阻抗出現突變,會引發信號反射、衰減、串擾等問題,輕則導致設備運行不穩定,重則造成數據傳輸錯誤、系統崩潰。尤其是在高頻(如 5G 基站、毫米波雷達)、高速(如 PCIe 5.0、DDR5)應用場景中,多層板的阻抗控制精度已成為衡量產品競爭力的核心指標之一。

多層板阻抗控制,是指通過設計線路結構、選擇合適基材、優化生產工藝等手段,將多層板中信號傳輸線路的阻抗值穩定在設計要求范圍內(通常為 50Ω、75Ω、100Ω 等標準值),確保信號在傳輸過程中 “阻抗匹配” 的技術。

簡單來說,阻抗可理解為信號傳輸時遇到的 “阻力”,當信號源、傳輸線路、負載的阻抗一致時,信號能最大限度地傳遞到負載端,避免反射損耗 —— 這就是阻抗控制的核心目標。

多層板的阻抗類型需根據信號傳輸方式和應用場景選擇,常見類型包括:

? 特性阻抗(Characteristic Impedance, Z0):單根信號線與參考平面(如 GND、Power 層)之間的阻抗,適用于單端信號傳輸,是多層板中最常用的阻抗類型,常見于射頻(RF)、視頻信號線路。

? 差分阻抗(Differential Impedance, Zdiff):兩根平行信號線之間的阻抗,適用于差分信號傳輸(如 USB、Ethernet、DDR)。差分阻抗又分為 “共模阻抗” 和 “差模阻抗”,實際設計中通常控制差模阻抗(如 100Ω、90Ω)。

? 奇模阻抗與偶模阻抗:差分信號傳輸中的細分參數,奇模阻抗指兩根信號線電流方向相反時的阻抗,偶模阻抗指電流方向相同時的阻抗,二者共同決定差分阻抗的最終值。

多層板的阻抗值并非由單一因素決定,而是受線路結構、基材特性、工藝精度等多維度參數影響,其中關鍵參數包括:

1. 線路幾何參數:線寬(W)、線距(S,差分線路專用)、線路厚度(T,即銅箔厚度),這些參數的微小偏差會直接導致阻抗值波動。

2. 基材參數:介質厚度(H,即信號線與參考平面之間的基材厚度)、介電常數(εr,基材的核心電學特性),介電常數越大,阻抗值越低;介質厚度越大,阻抗值越高。

3. 工藝參數:蝕刻精度(影響線寬一致性)、層壓壓力與溫度(影響介質厚度均勻性)、鍍銅厚度(影響線路厚度),這些工藝環節的控制精度決定了阻抗的批量穩定性。

多層板的信號線路可視為 “微帶傳輸線” 或 “帶狀線傳輸線”,其阻抗計算需基于傳輸線理論:

? 微帶傳輸線:信號線位于多層板表面,僅一側有參考平面(如頂層線路 + 第二層 GND),適用于表層信號傳輸,阻抗受空氣介電常數(ε0≈1)影響,計算時需考慮 “有效介電常數”(εeff)。

? 帶狀線傳輸線:信號線被夾在兩層參考平面之間(如第三層線路 + 第二層 GND + 第四層 Power),適用于內層信號傳輸,阻抗僅由基材介電常數決定,穩定性優于微帶傳輸線。

傳輸線理論的核心公式為:阻抗與介質厚度(H)、線寬(W)成正相關,與介電常數(εr)、線路厚度(T)成負相關。即:H 越大、W 越大,阻抗越高;εr 越大、T 越大,阻抗越低。

實際設計中,多層板阻抗計算需結合線路類型(微帶 / 帶狀線)選擇公式,或借助專業軟件(如 Polar SI9000、Cadence Allegro)進行仿真計算,以下為兩種常見線路的簡化計算邏輯:

當線路厚度 T 遠小于介質厚度 H(T/H < 0.1)時,簡化公式為:

Z0 ≈ (87 / √(εr + 1.41)) × ln(5.98H / (0.8W + T))

若 T/H ≥ 0.1,需考慮線路厚度對阻抗的影響,公式需引入修正項,此時更建議使用專業軟件計算(如 Polar SI9000 可自動修正線厚影響)。

當兩根差分線路對稱分布于兩層參考平面之間時,簡化公式為:

Zdiff ≈ 2 × (87 / √εr) × ln(1.9×(2H + T)/(0.8W + T))

若線路間距 S 較小(S < 3W),需考慮兩根線路之間的耦合效應,公式需增加耦合修正項,此時軟件仿真的精度遠高于手工計算。

1. 基材介電常數的選取:基材供應商提供的介電常數通常為 “典型值”,實際生產中需考慮頻率(高頻下介電常數會下降)、溫度(溫度升高介電常數略有上升)的影響,建議選取 “實際應用條件下的介電常數”(如 FR-4 基材在 1GHz 頻率下 εr≈4.2,而非常溫低頻下的 4.5)。

2. 工藝公差的預留:線寬、介質厚度在生產中會存在公差(如線寬公差 ±0.03mm,介質厚度公差 ±5%),計算時需將公差納入考量,例如設計目標阻抗 50Ω,需預留 ±10% 的公差范圍(即 45Ω~55Ω),避免批量生產時超出規格。

多層板阻抗控制并非單一工藝,而是覆蓋 “設計 - 基材 - 制作 - 檢測” 的全流程技術,每個環節的偏差都會累積影響最終阻抗精度,以下為關鍵工藝環節的控制要點:

設計是阻抗控制的 “源頭”,若設計參數不合理,后續工藝再精細也無法滿足要求,核心要點包括:

1. 阻抗類型與目標值確定:根據信號類型(單端 / 差分)、應用場景(高頻 / 高速)確定阻抗類型,例如 5G 射頻信號常用 50Ω 特性阻抗,DDR5 內存常用 100Ω 差分阻抗。

2. 線路結構與參數設計:借助 Polar SI9000 等軟件,輸入基材介電常數(εr)、介質厚度(H)、目標阻抗值,反向計算線寬(W)、線距(S),例如:FR-4 基材(εr=4.2)、介質厚度 H=0.2mm,目標 50Ω 特性阻抗,計算得線寬 W≈0.25mm。

3. 參考平面的合理布局:確保每根信號線路都有對應的參考平面(GND 或 Power 層),且參考平面無 “斷點”(如避免在信號線正下方開窗、挖槽),防止阻抗突變。

基材是阻抗控制的 “基礎載體”,其特性直接決定阻抗的穩定性,選擇要點包括:

1. 介電常數的穩定性:優先選擇介電常數波動小(±2% 以內)、高頻特性好的基材,例如高頻場景(5G、毫米波)可選用 PTFE基材(εr≈2.1,高頻下穩定性優于 FR-4),普通場景可選用高 Tg FR-4 基材(Tg≥170℃,溫度穩定性好)。

2. 介質厚度的公差控制:基材的介質厚度公差需≤±5%,例如設計介質厚度 0.2mm,需選擇公差≤±0.01mm 的基材,避免因厚度偏差導致阻抗超差。

3. 銅箔厚度的一致性:銅箔厚度(如 1oz=35μm、2oz=70μm)需與設計參數匹配,且同一批次銅箔的厚度公差≤±10%,防止線路厚度偏差影響阻抗。

線路是阻抗的 “直接載體”,線寬的微小偏差會導致阻抗大幅波動(通常線寬每偏差 0.01mm,阻抗偏差約 1Ω~2Ω),核心控制要點:

1. 菲林制作精度:菲林的線寬偏差需≤±0.005mm,采用高精度激光照排機制作菲林,避免因菲林偏差導致線路精度不足。

2. 曝光與顯影工藝:曝光能量需穩定(波動≤±5%),顯影時間需根據顯影液濃度、溫度調整(通常 25℃下顯影時間 60s~90s),確保顯影后線路邊緣無鋸齒、無殘膠,線寬偏差≤±0.01mm。

3. 蝕刻工藝控制:蝕刻液濃度(如 CuCl2 濃度 180g/L~220g/L)、溫度(45℃~50℃)、噴淋壓力(1.5bar~2.0bar)需穩定,采用 “蝕刻因子” 管控(蝕刻因子≥4,即線路側面垂直度好),避免因蝕刻過度導致線寬變小、阻抗升高,或蝕刻不足導致線寬變大、阻抗降低。

層壓是多層板 “分層合一” 的關鍵環節,直接影響內層線路的介質厚度(H)和均勻性,控制要點:

1. 層壓參數設定:根據基材類型設定層壓壓力(通常 25kg/cm2~35kg/cm2)、溫度(FR-4 基材層壓溫度 170℃~180℃)、時間(60min~90min),確保半固化片(PP)完全流動,填充線路間隙,形成均勻的介質層。

2. 層壓均勻性管控:采用 “均勻性測試板” 監控層壓后介質厚度的均勻性,同一板面的介質厚度偏差需≤±3%,避免因壓力不均導致局部介質厚度過薄(阻抗降低)或過厚(阻抗升高)。

3. 排氣控制:層壓過程中需及時排出空氣,避免產生氣泡,若介質層存在氣泡,會導致局部介電常數下降、阻抗升高,影響信號傳輸。

對于需要過孔的信號線路(如表層與內層信號互聯),孔壁鍍銅質量會影響阻抗一致性,控制要點:

1. 鉆孔精度:孔徑偏差需≤±0.01mm,孔位偏差≤±0.02mm,避免因孔徑過大導致鍍銅后孔壁厚度不足,影響阻抗。

2. 孔壁處理:鉆孔后需進行 “去鉆污”(采用堿性高錳酸鉀溶液)、“微蝕”(去除孔壁氧化層),確保孔壁與鍍銅層結合良好,避免因結合不良導致局部阻抗升高。

3. 鍍銅厚度控制:孔壁鍍銅厚度需≥20μm(滿足 IPC-6012 標準),且同一批次鍍銅厚度偏差≤±10%,確保孔壁阻抗與線路阻抗一致,避免過孔處阻抗突變。

阻抗檢測是阻抗控制的 “最后一道防線”,需覆蓋 “首件 - 量產 - 成品” 全流程,檢測要點:

1. 首件檢測:每批次生產前制作 “阻抗測試板”(與產品同結構、同工藝),采用阻抗測試儀(如 Agilent E5071C)測試阻抗值,若首件阻抗超差(如超出 ±10%),需調整工藝參數(如蝕刻時間、層壓壓力)后重新試產。

2. 量產抽檢:量產過程中每 200 塊板抽檢 1 塊,測試關鍵信號線路的阻抗值,監控阻抗的批量穩定性,若抽檢合格率低于 95%,需停機排查原因(如基材批次變化、蝕刻液老化)。

3. 成品全檢:對于高可靠性產品(如汽車電子、醫療設備),需對每塊成品板進行阻抗全檢,確保所有信號線路的阻抗值符合設計要求,避免不良品流入客戶端。

在實際生產中,多層板阻抗控制常面臨 “阻抗值偏差”“批量一致性差”“高頻下信號完整性不足” 等問題,以下為典型問題及解決方案:

1. 基材介電常數(εr)實際值高于設計值(如設計時按 εr=4.2,實際基材 εr=4.8);

2. 線寬實際值大于設計值(如設計線寬 0.25mm,實際線寬 0.28mm);

3. 介質厚度(H)實際值小于設計值(如設計 H=0.2mm,實際 H=0.18mm)。

1. 更換介電常數更低的基材,或重新計算線寬(如 εr=4.8 時,線寬調整為 0.22mm);

2. 優化蝕刻工藝,縮短蝕刻時間(如從 80s 調整為 70s),減小線寬偏差;

3. 更換介質厚度更大的基材,或調整層壓參數(如增加層壓壓力,減少介質厚度壓縮量)。

1. 基材批次間介電常數波動大(不同批次 εr 偏差 ±5%);

2. 蝕刻液濃度不穩定(濃度波動導致線寬偏差 ±0.02mm);

3. 層壓壓力分布不均(同一層壓盤中不同位置的介質厚度偏差 ±0.03mm)。

1. 對每批次基材進行介電常數檢測,僅使用偏差≤±2% 的基材;

2. 實時監控蝕刻液濃度,每 2 小時檢測一次,濃度不足時及時補充;

3. 采用 “分區壓力監控” 的層壓機,確保層壓盤中各位置壓力偏差≤±2%,或在層壓前在測試板上放置多個厚度傳感器,監控介質厚度均勻性。

1. 基材高頻介電常數穩定性差(低頻下 εr=4.2,10GHz 下 εr=3.8,導致阻抗升高);

2. 線路表面粗糙度大(銅箔表面粗糙度 Ra=5μm,高頻下趨膚效應明顯,阻抗升高);

3. 參考平面接地不良(高頻下接地阻抗升高,導致信號反射)。

1. 選用高頻特性好的基材,如 PTFE(εr=2.1,10GHz 下波動≤±1%)或陶瓷填充基材(如羅杰斯 RO4350,高頻下介電常數穩定);

2. 采用低表面粗糙度銅箔(Ra≤1μm 的 “極薄銅箔”),減少趨膚效應帶來的阻抗升高;

3. 增加接地過孔密度(如每 5mm 布置一個接地過孔),確保參考平面接地良好,降低接地阻抗。

不同行業對多層板阻抗控制的精度、穩定性要求差異較大,以下為典型應用場景:

? 5G 通信設備:基站天線、RRU(射頻拉遠單元)的多層板需控制 50Ω 特性阻抗,精度要求 ±5%,且高頻(28GHz 毫米波)下阻抗穩定性需≤±3%,避免信號衰減導致通信距離縮短。

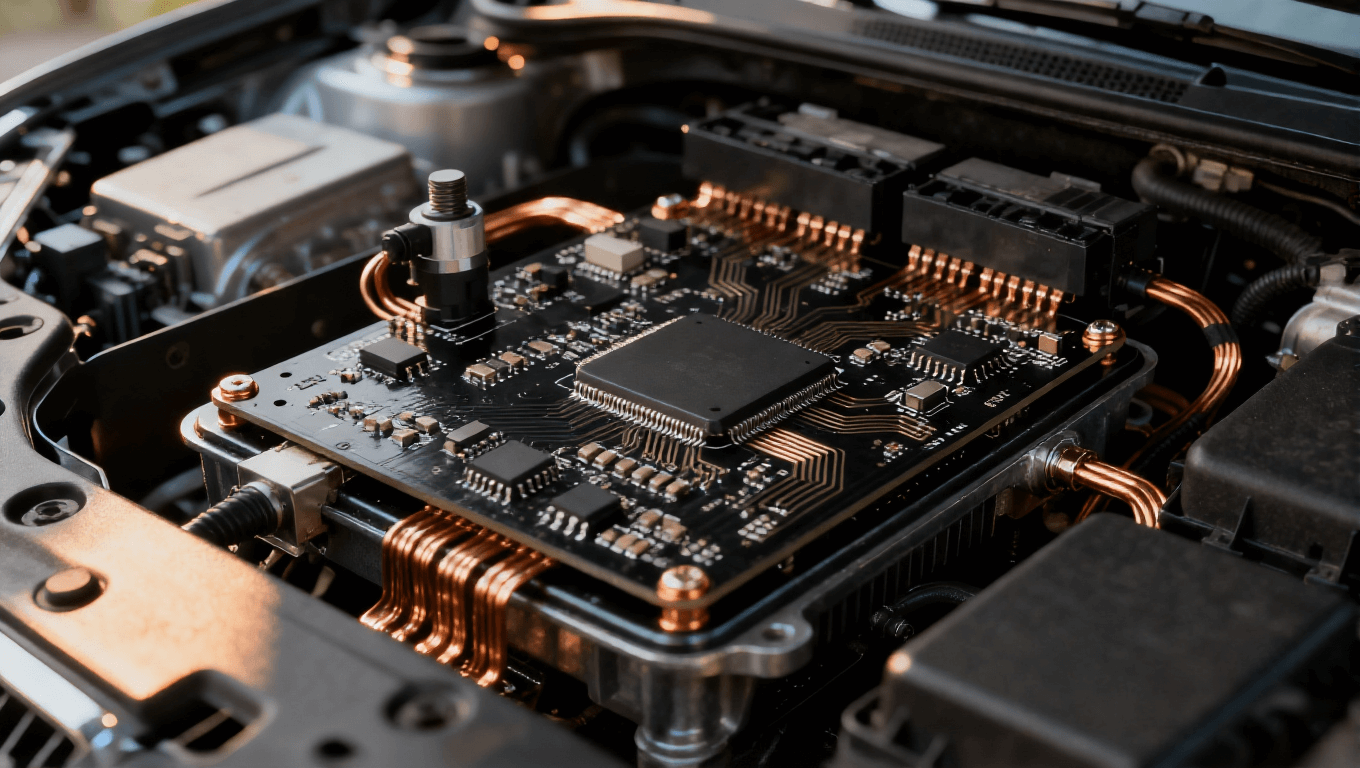

? 汽車電子:ADAS(高級駕駛輔助系統)的雷達板(如 77GHz 毫米波雷達)需控制 100Ω 差分阻抗,精度 ±8%,且耐高溫(-40℃~125℃)下阻抗波動≤±5%,確保極端環境下雷達信號穩定。

? 工業控制:PLC(可編程邏輯控制器)的多層板需控制 75Ω 特性阻抗(用于模擬信號傳輸),精度 ±10%,且抗干擾能力強,避免工業現場電磁干擾導致阻抗突變。

? 醫療設備:超聲診斷儀、監護儀的多層板需控制 50Ω 或 100Ω 阻抗,精度 ±7%,且生物相容性好(基材無有害物質釋放),確保設備安全穩定運行。

隨著電子設備向 “高頻化、高速化、小型化” 發展,多層板阻抗控制技術也在不斷升級,未來趨勢包括:

1. 高精度化:阻抗控制精度從當前的 ±10% 向 ±5% 甚至 ±3% 升級,滿足 112Gbps 高速信號(如 PCIe 6.0)的傳輸需求;

2. 新材料應用:新型低介電常數基材(如 εr<2.0 的碳納米管復合材料)、耐高溫基材(Tg>250℃的 PI 基材)將逐步普及,提升阻抗穩定性和環境適應性;

3. 智能化管控:引入 AI 技術實現阻抗全流程智能監控,如通過機器視覺自動檢測線寬偏差,結合大數據分析預測阻抗變化趨勢,提前調整工藝參數;

4. 集成化設計:將阻抗控制與 “埋阻、埋容” 技術結合,在多層板內部集成電阻、電容元件,減少外部元件帶來的阻抗突變,提升信號完整性。

多層板阻抗控制技術是保障電子設備信號完整性的核心技術,其涵蓋 “理論計算 - 設計定義 - 工藝管控 - 檢測驗證” 全流程,需從基材選擇、線路制作、層壓工藝等多個環節精準把控。隨著 5G、汽車電子、工業控制等行業的快速發展,對多層板阻抗控制的精度、穩定性要求將持續提升,推動技術向高精度化、新材料化、智能化方向升級。

對于企業而言,掌握多層板阻抗控制技術不僅能提升產品競爭力,更能滿足高端電子設備的國產化需求 —— 未來,需進一步加強技術研發,優化工藝流程,實現多層板阻抗控制技術的自主可控,為電子信息產業的高質量發展提供支撐。