在高速數(shù)字電路與射頻領(lǐng)域,信號(hào)傳輸速率已突破 GHz 級(jí)別,PCB 導(dǎo)通孔中的殘樁(Stub)成為信號(hào)完整性的主要威脅之一。背鉆(Back Drilling)工藝通過(guò)精準(zhǔn)去除多余銅柱,有效抑制信號(hào)反射與損耗,是高端 PCB 制造的核心技術(shù)。本文從設(shè)計(jì)規(guī)范、工藝控制、檢測(cè)方法三大維度,深度解析背鉆工藝的實(shí)施要點(diǎn)。

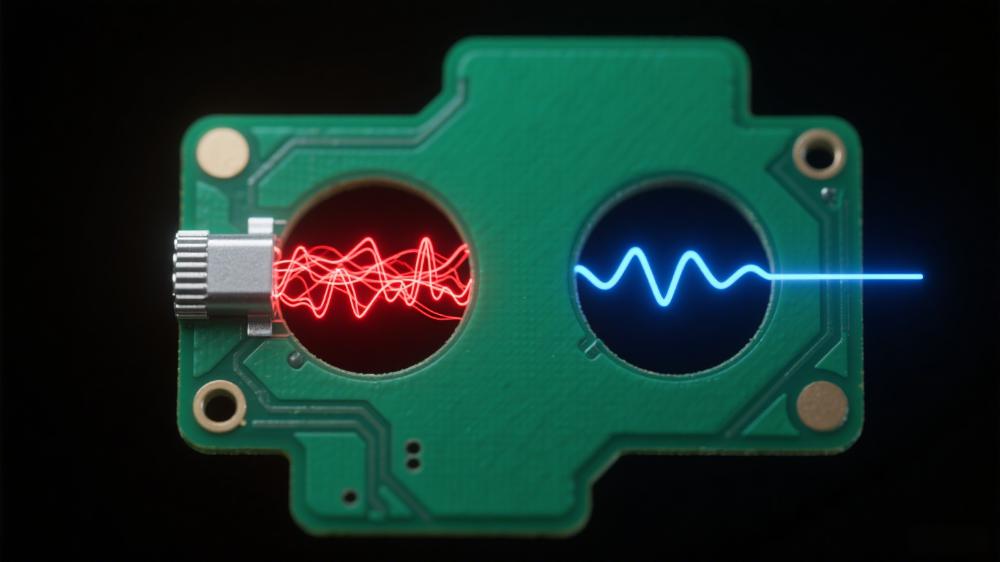

背鉆是針對(duì)多層 PCB 通孔的二次鉆孔工藝,其核心目的是去除未連接層的銅質(zhì)殘樁(Stub)。當(dāng)信號(hào)通過(guò)通孔傳輸時(shí),Stub 會(huì)引發(fā)信號(hào)反射、諧振及衰減,尤其在 10Gbps 以上高速場(chǎng)景中,Stub 長(zhǎng)度超過(guò) 10mil 即可導(dǎo)致顯著信號(hào)失真。

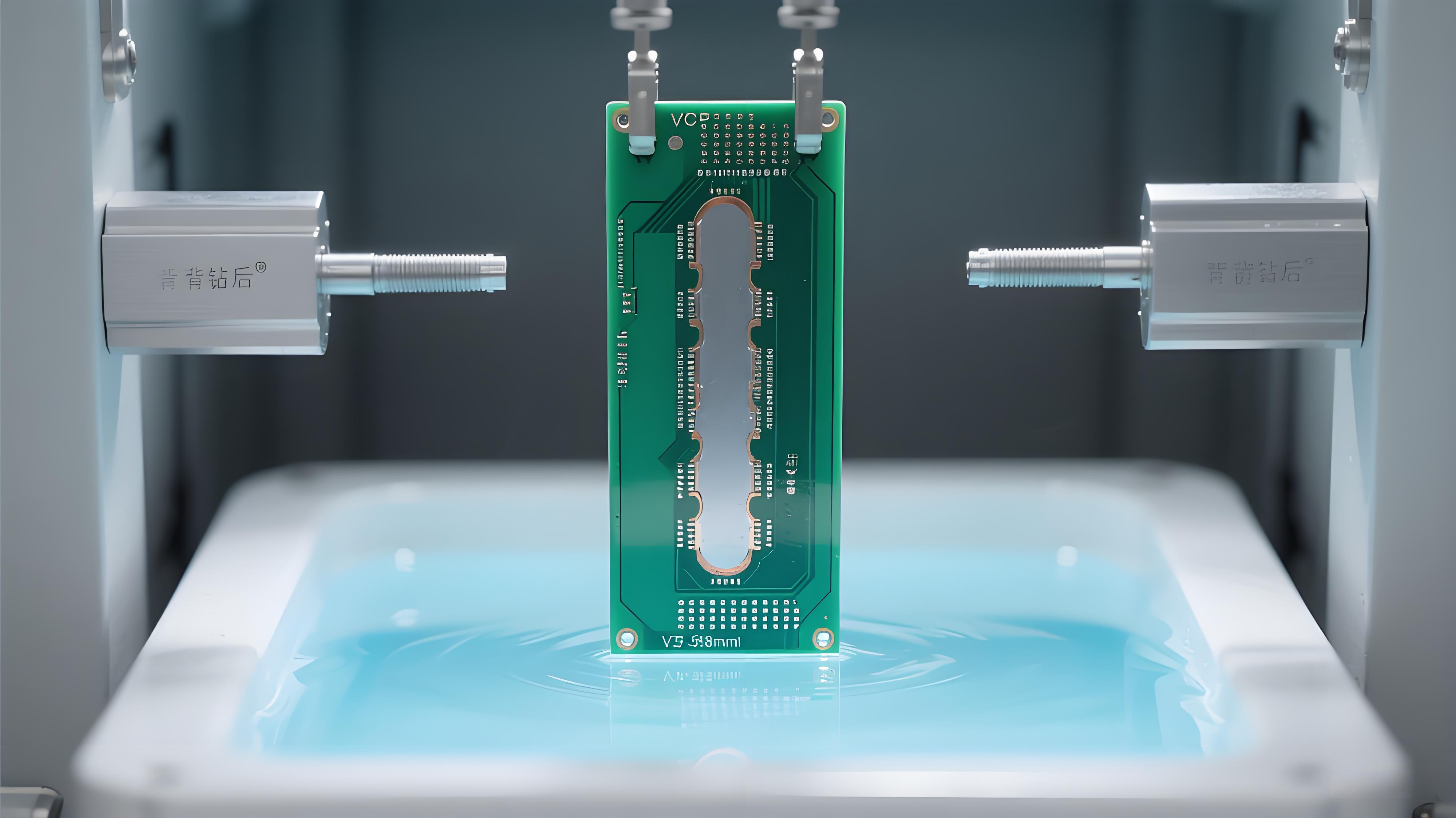

背鉆工藝通過(guò)以下步驟實(shí)現(xiàn):

1. 首次鉆孔:完成通孔鉆削與電鍍,形成全板連接。

2. 二次背鉆:從板面反向鉆孔,使用更大直徑鉆頭(通常比原孔大 0.15–0.3mm)鉆至目標(biāo)層附近,保留 50–150μm 殘樁(B 值)以平衡精度與安全性。

3. 殘樁處理:通過(guò)化學(xué)蝕刻或等離子清洗進(jìn)一步縮短殘樁至 20μm 以下,減少信號(hào)損耗。

背鉆深度是工藝成功的關(guān)鍵,需通過(guò)嚴(yán)格計(jì)算與補(bǔ)償實(shí)現(xiàn):

? 計(jì)算公式:背鉆深度 = PCB總厚度 - 終止層至鉆入面距離 + 工藝補(bǔ)償值(通常0.05–0.15mm)。

? 公差要求:高頻板需控制深度偏差在 ±0.025mm 內(nèi),常規(guī)板卡需滿足 ±0.05mm。

? 設(shè)計(jì)標(biāo)注:文件中需明確標(biāo)注目標(biāo)層(如 L1-L5)、允許誤差及補(bǔ)償值,避免過(guò)深擊穿內(nèi)層或過(guò)淺殘留 Stub。

? 孔徑匹配:背鉆孔徑需大于原孔 0.15–0.3mm(推薦 0.2mm),確保完全移除 Stub 銅層。

? 安全間距:背鉆孔與周邊線路、銅皮需保持≥0.1mm 間距,防止鉆孔偏差導(dǎo)致短路。

? 布局優(yōu)化:同一區(qū)域背鉆深度差異不宜過(guò)大,減少鉆機(jī)參數(shù)調(diào)整頻率,提升效率。

? 介質(zhì)厚度:背鉆層間介質(zhì)厚度需≥0.17mm,且公差控制在 ±10% 以內(nèi)。

? 基材選擇:高 Tg 材料(如 170℃ Tg FR4)可提升層壓精度;陶瓷或金屬芯板需特殊參數(shù)設(shè)計(jì)。

? 板材平整度:壓合后板厚波動(dòng)需≤±0.05mm,避免深度計(jì)算誤差。

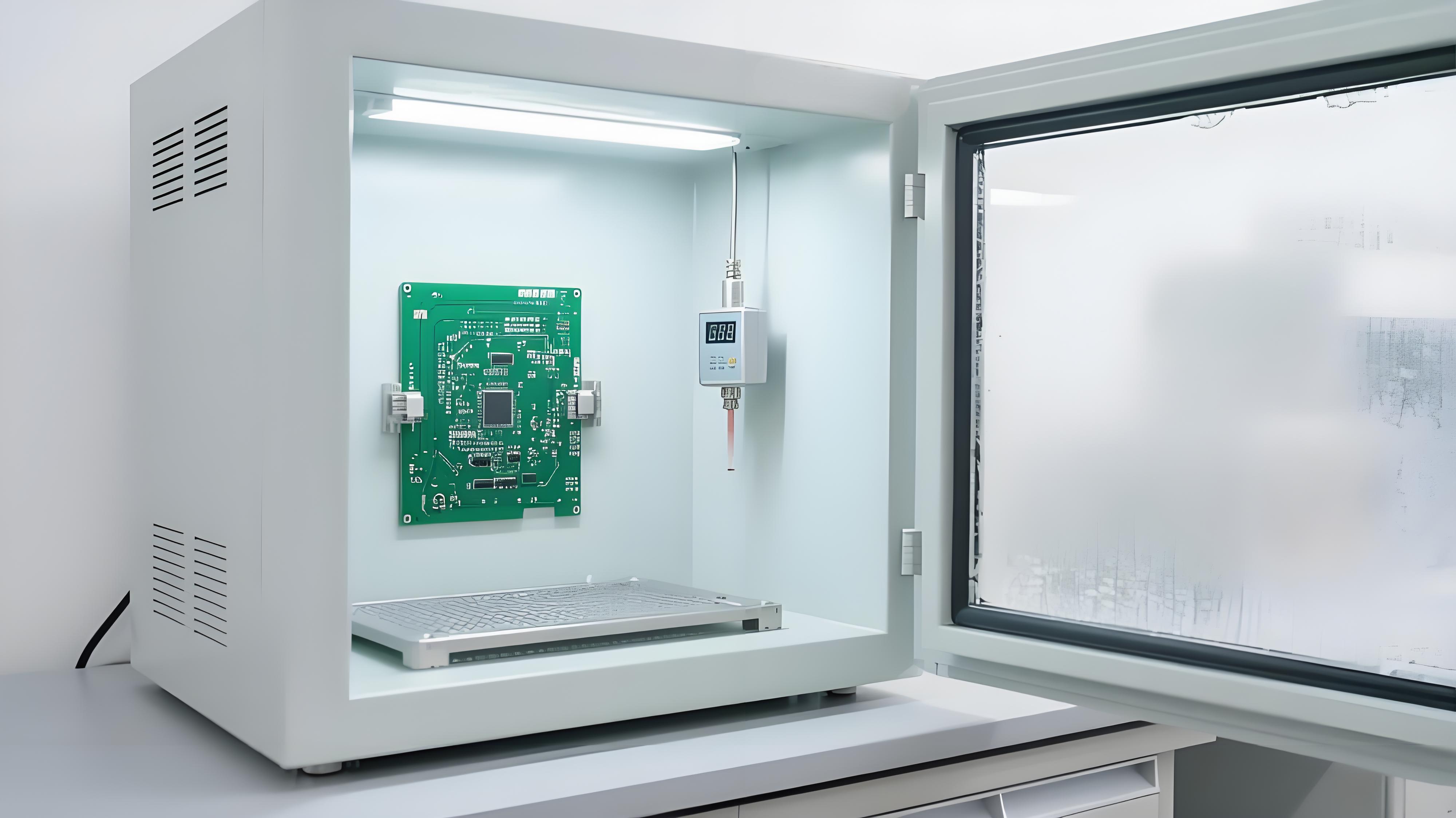

? 高精度鉆機(jī):需配備 Z 軸定位精度≤±0.01mm、光柵尺 / 激光傳感器的設(shè)備,支持實(shí)時(shí)深度修正。

? 鉆頭選擇:鉆尖角度 130°–165°(常用 150°),角度越小排屑越易但控深能力越差。

? 工藝參數(shù):

? 下鉆速度:0.5–1.2m/min

? 鉆頭壽命:≤800hit(鎢鋼鉆頭)

? 溫度控制:分段冷卻(前段常溫,中段 - 10℃低溫)。

? 板厚測(cè)量:每板取≥3 點(diǎn)測(cè)量實(shí)際厚度,補(bǔ)償壓合公差。

? 鉆頭校準(zhǔn):新鉆頭需用長(zhǎng)度測(cè)量?jī)x(精度 ±0.001mm)校準(zhǔn),每 500 孔復(fù)檢磨損量。

? 導(dǎo)電蓋板:采用鋁片或覆銅板作為蓋板,厚度≤0.2mm,確保鉆深起點(diǎn)一致性。

? 電鍍控制:采用 VCP 垂直電鍍,電流密度 1.0–1.3ASD,時(shí)間 10–13min,確保孔銅厚度 5–8μm。

? 殘?jiān)幚?/span>:二次除膠 + 等離子清洗,避免化學(xué)藥水殘留。

? 烘干工藝:背鉆孔向下放置,100–110℃烘干,速度 1–1.5m/min,減少氧化。

? 實(shí)時(shí)傳感:接觸式深度傳感器觸發(fā)鉆深起點(diǎn),超差 ±0.03mm 自動(dòng)停機(jī)。

? 溫度監(jiān)測(cè):紅外測(cè)溫監(jiān)控鉆區(qū)溫度(閾值 150℃),防止鉆頭堵塞導(dǎo)致偏差。

? 切片分析:首件金相切片測(cè)量 Stub 長(zhǎng)度(要求≤0.05mm)及孔底至內(nèi)層距離(≥0.03mm)。

? X-Ray 檢測(cè):批量抽檢孔底與目標(biāo)層對(duì)齊情況,效率高于切片。

? 阻抗測(cè)試:高頻信號(hào)孔阻抗偏差需≤±5Ω(目標(biāo) 50Ω),間接驗(yàn)證 Stub 殘留。

? 國(guó)軍標(biāo) GJB 要求:依據(jù) SJ 21554-2020 標(biāo)準(zhǔn),環(huán)境溫度 15–35℃、濕度≤75%,設(shè)備需具備電信號(hào)傳感控深裝置。

? IPC 規(guī)范:背鉆孔壁需無(wú)毛刺、銅絲殘留,并通過(guò)飛針測(cè)試驗(yàn)證電氣連接。

? 核心領(lǐng)域:5G 基站、服務(wù)器主板、高速網(wǎng)絡(luò)設(shè)備(400G/800G 光模塊)、航空航天電子。

? 厚板挑戰(zhàn):板厚≥3mm 時(shí)需分步背鉆(如 2mm 分兩次鉆削),減少應(yīng)力變形。

? 成本權(quán)衡:背鉆增加約 20–30% 制造成本,需通過(guò)設(shè)計(jì)優(yōu)化(如避免盲埋孔冗余)平衡性價(jià)比。

背鉆工藝是高頻 PCB 信號(hào)完整性保障的核心手段,其成功實(shí)施依賴于全鏈條管控:

? 設(shè)計(jì)端:精準(zhǔn)計(jì)算深度、孔徑及間距,明確標(biāo)注終止層與公差;

? 制造端:采用高精度設(shè)備、嚴(yán)格參數(shù)控制及實(shí)時(shí)監(jiān)測(cè);

? 檢測(cè)端:結(jié)合切片、X-Ray 及阻抗測(cè)試實(shí)現(xiàn)多維驗(yàn)證。

通過(guò)遵循上述規(guī)范,背鉆工藝可顯著提升 10Gbps 以上高速電路的可靠性,為 5G、AI 計(jì)算及高端通信設(shè)備提供硬件基礎(chǔ)。未來(lái),隨著材料技術(shù)與設(shè)備精度的持續(xù)提升,背鉆工藝有望進(jìn)一步突破 ±0.01mm 精度極限,賦能下一代電子系統(tǒng)創(chuàng)新。了解更多歡迎聯(lián)系IPCB(愛(ài)彼電路)技術(shù)團(tuán)隊(duì)